Modern artificial intelligence thrives on raw computational power. Complex neural networks require specialised hardware to handle millions of simultaneous calculations. This demand has transformed graphics processing units into essential tools for researchers and developers alike.

Traditional processors struggle with the matrix mathematics underpinning neural network training. Unlike their sequential approach, parallel architectures in modern GPUs execute thousands of operations concurrently. This capability dramatically reduces training times for image recognition systems and language models.

Leading frameworks like TensorFlow and PyTorch now integrate GPU acceleration as standard. Developers benefit from 40-50x faster processing compared to CPU-based systems when training complex models. Such performance gains enable real-time applications in healthcare diagnostics and autonomous vehicle systems.

The evolution of dedicated tensor cores in newer GPU models further optimises AI workloads. These enhancements allow organisations to scale operations without prohibitive energy costs. For businesses investing in machine learning solutions, selecting appropriate hardware remains critical for maintaining competitive advantage.

Current advancements continue pushing boundaries in natural language processing and generative AI. As model complexity grows, so does reliance on high-performance computing solutions. Choosing the right graphics processing infrastructure now determines tomorrow’s technological breakthroughs.

Understanding GPU Architecture for Deep Learning

At the heart of accelerated artificial intelligence lies a meticulously engineered framework designed for parallel tasks. Unlike conventional processors, modern graphics units employ streaming multiprocessors that juggle thousands of computational threads simultaneously. This design philosophy transforms complex matrix operations into manageable parallel workloads.

Core Components Explained

Each streaming multiprocessor operates using warps – bundles of 32 threads executing instructions in lockstep. With 32 active warps per SM, architects achieve concurrent processing of 1,024 threads. Resources like registers and memory bandwidth are dynamically allocated between warps, ensuring optimal utilisation.

Architectural Evolution

Recent innovations like NVIDIA’s Ada Lovelace architecture demonstrate tangible progress. Its redesigned SM clusters deliver double the performance in AI simulations compared to previous generations. Similarly, Ampere architecture introduced CUDA cores capable of twice the FP32 operations per cycle, dramatically accelerating training workflows.

Developers now benefit from six successive architecture generations – Pascal to Hopper – each refining memory hierarchies and compute densities. These advancements enable neural networks to process 8-bit integer operations 20x faster than traditional FP32 calculations.

Understanding these architectural nuances helps teams select hardware balancing tensor core counts, memory bandwidth, and power efficiency. Such decisions directly influence model training speeds and inference accuracy in real-world applications.

What is deep learning gpu

Specialised hardware drives modern AI breakthroughs, particularly in handling neural network operations. These processors combine enhanced memory architectures with computational designs tailored for matrix-heavy tasks. Manufacturers now produce distinct variants optimised for either consumer applications or enterprise-scale artificial intelligence projects.

Defining the Term and Its Relevance

Neural network accelerators differ fundamentally from standard graphics cards through three critical features:

- Expanded memory capacity: Enterprise solutions like NVIDIA’s Tesla series offer 80GB VRAM for large datasets

- Enhanced precision support: Dedicated tensor cores enable mixed-precision arithmetic for faster model training

- Software optimisation: Drivers specifically tuned for frameworks like PyTorch accelerate development cycles

Consumer-grade alternatives such as GeForce RTX cards remain viable for smaller-scale projects. Their GDDR6X memory and CUDA core configurations still outperform traditional processors for most machine intelligence tasks. However, thermal limitations and smaller VRAM pools constrain their utility with billion-parameter models.

Organisations must evaluate workload requirements against hardware capabilities. Projects involving real-time video analysis or generative systems typically demand enterprise-grade resources. Conversely, prototype development or educational purposes often succeed with consumer hardware, provided developers implement memory optimisation techniques.

Decoding Tensor Cores and Matrix Multiplication

Matrix operations form the backbone of modern AI systems, demanding hardware that crunches numbers at blistering speeds. Specialised tensor cores tackle this challenge through architectural innovations specifically engineered for parallel matrix maths. These components represent a paradigm shift in how processors handle neural network workloads.

Role of Tensor Cores in Accelerated Computations

Traditional processing units require hundreds of cycles for basic matrix multiplication. Tensor cores slash this through fused multiply-add operations that complete 4×4 matrix calculations in single cycles. Fourth-generation variants now handle eight different precision formats, from FP64 to INT8.

| Operation Type | CUDA Cores | Tensor Cores |

|---|---|---|

| 32×32 Matrix Multiply | 504 cycles | 235 cycles |

| FP16 Training Throughput | 24 TFLOPS | 312 TFLOPS |

| FP8 Inference Speed | N/A | 2x Faster |

Comparison with Conventional Cores

While standard CUDA cores excel at diverse tasks, they lack dedicated circuitry for bulk matrix operations. Tensor cores achieve 83% faster processing for transformer models according to NVIDIA benchmarks. As one engineer notes:

“The latest Hopper architecture delivers 4.8x better energy efficiency per matrix operation compared to previous designs.”

Modern gpus strategically combine both core types – tensor units handle intensive maths while conventional cores manage data movement. This hybrid approach enables real-time processing for applications ranging from medical imaging to financial forecasting.

Memory Bandwidth and Cache Hierarchy in GPUs

Neural network acceleration relies as much on memory design as computational power. Modern architectures employ a layered approach to data handling, balancing capacity against access speeds. This hierarchy directly impacts how quickly models process information during training and inference.

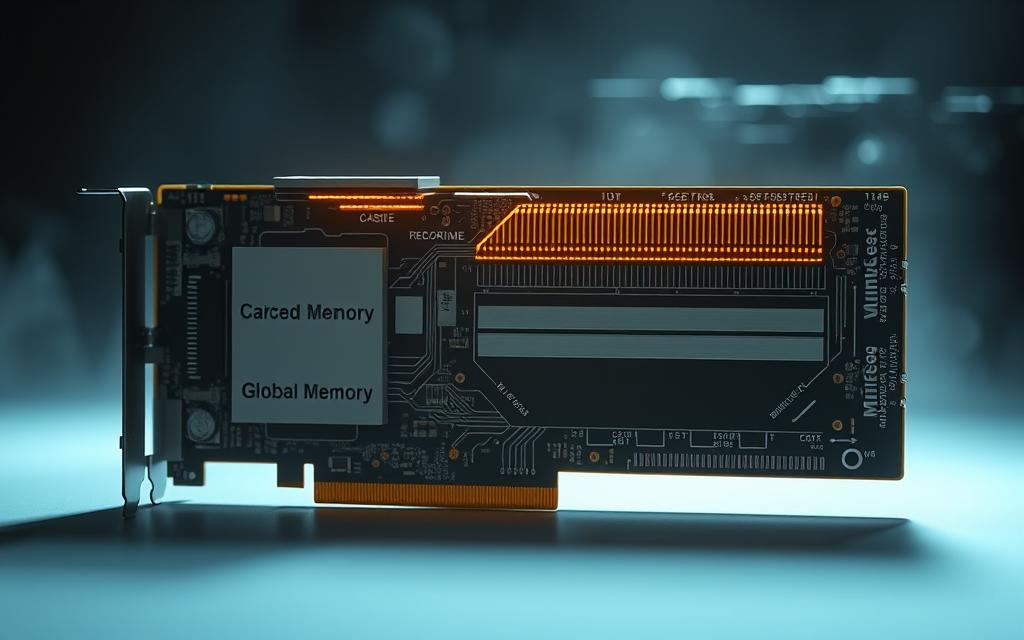

Global Memory vs Shared Memory

Global memory offers vast storage but suffers from high latency – up to 380 cycles for data retrieval. Shared memory operates 10x faster but provides limited capacity. Engineers must strategically allocate data pipelines between these tiers to prevent bottlenecks.

| Memory Type | Latency (cycles) | Bandwidth Impact |

|---|---|---|

| Global | 380 | 1,555 GB/s (A100) |

| L2 Cache | 200 | 6-72 MB capacity |

| L1/Shared | 34 | ~20 TB/s effective |

Recent architectural shifts prioritise cache expansion. NVIDIA’s Ada Lovelace design increased L2 cache to 72MB – 12x larger than previous generations. This change reduces global memory calls, accelerating matrix operations by 1.5-2x in transformer models.

Developers should match batch sizes to available memory bandwidth. Larger models like GPT-3 require 1.5TB/s+ throughput to keep tensor cores active. Memory coalescing techniques and optimal data layouts become critical when working with billion-parameter networks.

GPU vs CPU: Deep Learning Performance Insights

Computational demands of modern neural networks reveal stark contrasts between processor architectures. While traditional CPUs excel at sequential tasks, their parallel processing limitations become apparent when handling matrix-heavy operations. This fundamental difference explains why organisations prioritise GPU-based systems for large-scale model training.

Benchmarks demonstrate 50-100x faster execution for convolutional neural networks on graphics processors. A single high-end GPU can process 2,304 simultaneous threads versus 64 threads in modern server CPUs. This parallelism proves critical when training vision models with millions of parameters.

Memory bandwidth further widens the performance gap. NVIDIA’s A100 delivers 1,555GB/s throughput – 15x higher than AMD’s EPYC 9654 CPU. Such capacity enables real-time analysis of 4K video streams, a common requirement in autonomous systems development.

Central processors retain value in specific scenarios:

- Data preprocessing requiring complex branching logic

- Small-scale prototyping with limited datasets

- Hybrid workflows combining CPU-based input handling with GPU acceleration

Recent innovations like Intel’s Advanced Matrix Extensions aim to narrow this divide. However, energy efficiency metrics still favour graphics processors, with 3.2x better performance-per-watt in transformer model training according to 2023 benchmarks.

Organisations must balance hardware costs against operational requirements. While initial GPU investments appear steep, their throughput advantages often justify expenditure for production-scale systems. Strategic resource allocation between processor types maximises both speed and cost-effectiveness.

Optimising GPUs for Deep Neural Network Training

Maximising hardware potential requires strategic adjustments across computational layers. Modern architectures like NVIDIA’s Ada Lovelace and Hopper introduce features that slash idle cycles while boosting data throughput. Developers achieve these gains through both hardware utilisation and software refinements.

Techniques to Reduce Latency

Asynchronous memory transfers prove vital for performance gains. RTX 40 series cards complete second global memory reads in 165 cycles – 17.5% faster than traditional methods. The H100’s Tensor Memory Accelerator merges data prefetching with index calculations, cutting matrix multiplication times by 15%.

Three critical practices enhance efficiency:

- Matching CUDA versions to hardware capabilities

- Prioritising GPU-native libraries like cuDNN

- Balancing batch sizes against available memory bandwidth

Enhancing Throughput with Asynchronous Copies

Modern frameworks leverage parallel data pipelines to keep tensor cores active. Gradient accumulation techniques enable larger effective batch sizes without exhausting VRAM. Combined with mixed-precision training, these methods accelerate convergence while maintaining numerical stability.

Monitoring tools like NVIDIA Nsight Systems reveal hidden bottlenecks. One engineer noted:

“Kernel fusion strategies improved our transformer training speeds by 22% through reduced memory transactions.”

Distributed training setups benefit from NVLink interconnects, which maintain 89% scaling efficiency across eight GPUs. Such optimisations prove essential when deploying billion-parameter models in production environments.

Practical Performance Estimates: Ada and Hopper Architectures

Cutting-edge neural network implementations demand precise hardware evaluations. NVIDIA’s Hopper architecture demonstrates 1.9x faster Llama2 70B inference versus previous designs, while Ada Lovelace’s enlarged 72MB L2 cache accelerates transformer models by 2x. These improvements stem from redesigned tensor core configurations and enhanced memory hierarchies.

Real-world tests reveal concrete scaling benefits. Doubling batch sizes boosts throughput by 13.6% across convolutional and transformer-based learning models. Eight H100 systems achieve 5% lower communication overhead than V100 clusters through NVLink 3.0 enhancements. Such gains prove critical for time-sensitive applications like real-time translation services.

Energy efficiency remains paramount in production environments. Hopper’s fourth-gen tensor cores deliver 4.8x better performance-per-watt in matrix operations compared to Ampere designs. Combined with mixed-precision support, these cores enable sustainable scaling of billion-parameter networks without prohibitive power costs.

Organisations must weigh architectural strengths against project requirements. While Ada excels in memory-bound tasks, Hopper dominates raw computational throughput. Strategic hardware selection now determines feasibility for next-generation AI implementations across industries.

FAQ

Why are GPUs preferred over CPUs for deep learning tasks?

Parallel processing capabilities enable GPUs to handle thousands of threads simultaneously, accelerating matrix multiplication and other compute operations central to deep neural networks. This contrasts with CPUs, which prioritise sequential tasks, resulting in slower training times for complex models.

What role do tensor cores play in accelerating deep neural networks?

A: Tensor cores specialise in executing mixed-precision calculations, optimising matrix operations like those in transformer architectures. Found in NVIDIA’s Volta or Ampere GPUs, they boost throughput by up to 12x compared to conventional cores, making them vital for real-time applications like video analytics.

How does memory bandwidth affect model training efficiency?

Higher memory bandwidth allows faster data transfer between GPU memory and processing units, reducing bottlenecks during training. For instance, NVIDIA’s H100 employs 3TB/s bandwidth, enabling rapid handling of large datasets. Insufficient bandwidth can stall computations, increasing latency.

Can multiple GPUs improve performance in data centres?

Yes, scaling across multiple GPUs via frameworks like TensorFlow or PyTorch distributes workloads, cutting training times. However, data centres must manage power consumption and communication overhead between devices. Solutions like NVIDIA’s NVLink mitigate latency, enhancing performance for cloud-based projects.

What are the advantages of using cloud-based GPUs for machine learning projects?

A: Cloud platforms like AWS or Azure offer scalable access to high-end GPUs, eliminating upfront hardware costs. They support dynamic workloads, from image recognition to natural language models, while providing tools for optimising resource allocation. However, latency-sensitive applications may require on-premises units.

How do Ada and Hopper architectures differ in handling AI workloads?

NVIDIA’s Hopper architecture introduces advanced tensor cores and transformer engine features, targeting large-scale data centre deployments. Ada Lovelace GPUs, meanwhile, focus on energy efficiency and performance per watt, ideal for edge computing or smaller-scale operations like medical imaging.